One of the projects I was working on once required a doubling of clock speed from an Arduino Nano, which has an Atmel 328p running at 16 MHz on-board. I'm going to explain in this piece how I was able to double clock frequency with digital logic - no PLL or DLL needed!

My challenge? I wanted to do it only with parts on hand, and preferably with digital logick. And, no, overclocking the Arduino or changing the clock in general wasn't a path I was willing to go down.

(Plus - where's the fun in that?)

If you really want to multiple clocks, use a PLL.

If you want the glory of using 7400 series gates in ways they weren't built to be used? You're reading the right post!

How Did You Double Clock Frequency with Digital Logic? Isn't That Impossible?

First, not that it matters for the project (but in the circuit section you certainly will care about how I tuned it for 32 MHz), but I first set the fuses on the 328p to produce a buffered clock on pin 8 (labeled D8 on the Uno/Nano - search 'CKOUT' in the 328P data sheet for more).

Now, I mentioned above that I didn't want to use analog components - but, alas, we exist in reality.

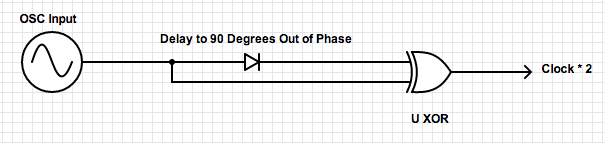

"Analog" effects dictate everything in engineering, and digital logic is no different, however much it wants to pretend life is all 1s and 0s. My goal was, therefore, to produce a second clock 90 degrees out of phase with the original. I'd use the delay inherent in digital components to get a phase shift then XOR the two clocks together.

What's an XOR?

For the uninitiated, XOR, or exclusive or, is a function which will return 'true' when and odd number of inputs are 'true'.

For a two input XOR function, that means only one will be high. Don't worry, I drew it for you:

So, the clock will be high when only one of the two out of phase clocks is high... which happens to be twice as often as the original clock.

And that's the theory, which again I've conveniently drawn for you here:

How Did Clock Doubling Work in Reality?

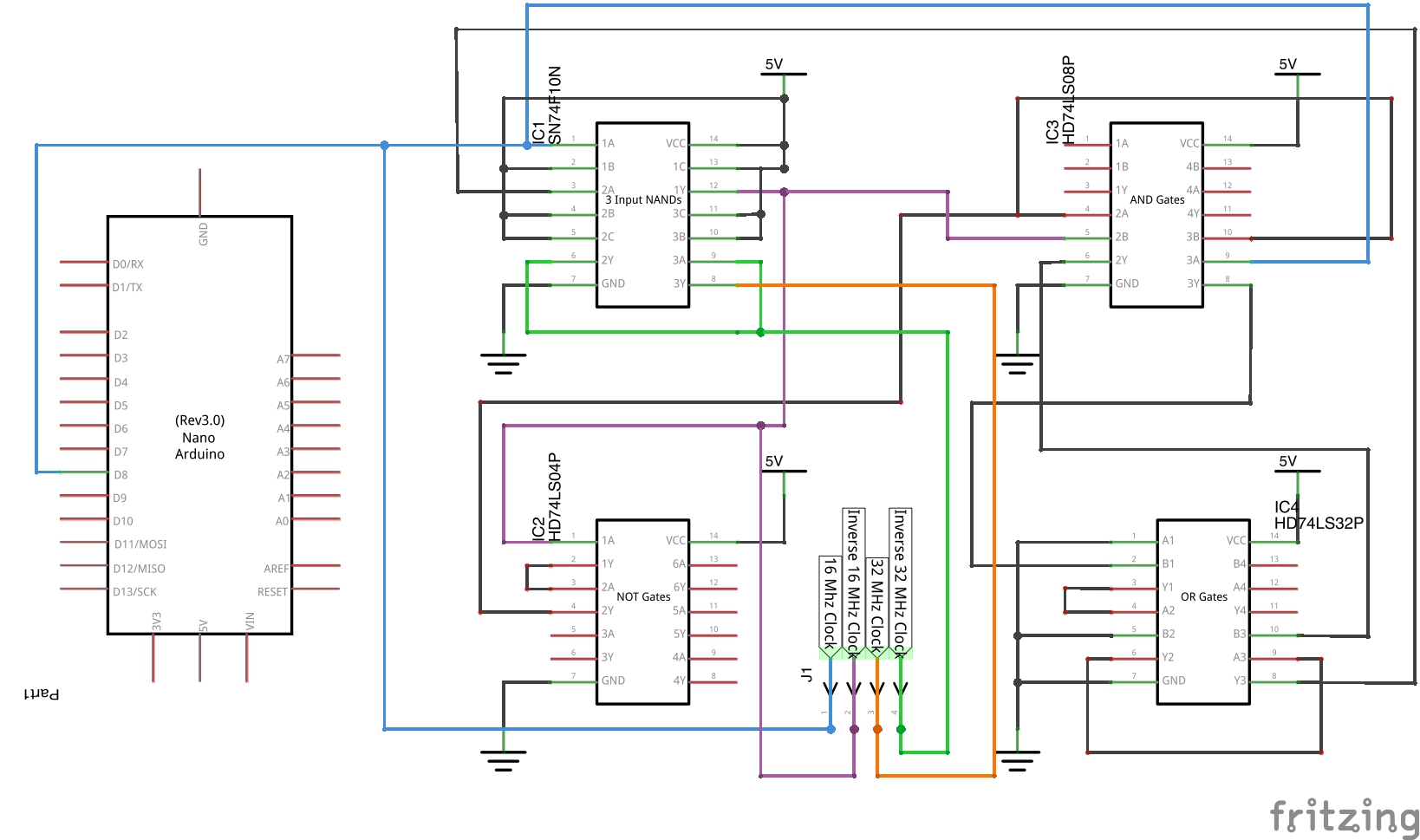

The actual implementation details were particularly hilarious. I did have a not gate - the perfect gate to add delay. However, I didn't have an XOR!

Well, you can always get around things like that: (A AND !B) OR (B AND !A) did the trick.

I also needed a very fast gate to handle the 32 MHz signal - which is approaching the limits for the 74LS parts I mostly had handy.

So, here's my actual parts list:

- HD74LS04P - Not Gate. Delay

- HD74LS08P - And Gate. XOR

- HD74LS32P - Or Gate. XOR

- SN74F10N - 3 Input Nand Gates. Clean up the ugly clock from the hacked XOR

Here's the schematic, drawn to the best of my ability.

Note: I can't take responsibility if you break something by using this information, somehow. Your mileage will almost certainly vary, as actual time delays will vary from part to part.

This is the combination which worked best to get a usable clock out of the 74LS32 for me. I then cleaned up with the very fast (in comparison) 74F10N.

Note that I'm using the 74F10N as a not gate - merely tying unused inputs to high.

And, because I know you're interested in seeing that rats nest wired up, you should find that over to the right somewhere.

Did Your Digital Clock Doubler Hack Produce a Beautiful 32 MHz Square Wave?

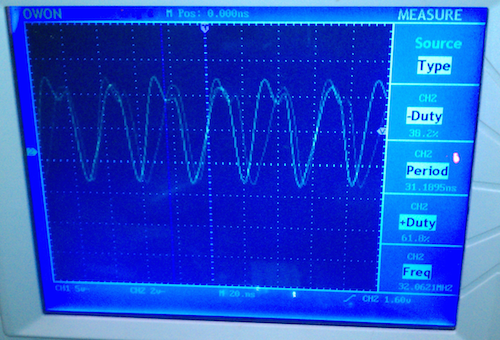

No, it was quite ugly in fact.

Of course, it was good enough for our purposes. The duty cycle moves between 50% and 60% high, but the project it went into appears stable even with the sloppy clock.

Here's a picture of my oscilloscope for internet points™ and some hard proof that this scheme worked:

Further Reading

If you just need a usable clock, this will work. Don't use it in any sort of mission critical application - I'll be replacing this with a real circuit later. For proof of concept, it worked well.

For budding EEs, read about what others have said about trying to double clock frequency with digital logic:

So, don't use it at work, you'll be laughed at. Don't use it in a product, you'll likely face reliability issues - and you'll pull your hair out when you need to substitute parts.

But, hey, when you're too lazy to use the right part/build the right circuit... it works in a pinch.